Current-Mode Analog-to-Digital Converters (iADC)

5 US Patents Issued & Proof of Silicon (Test Forthcoming)

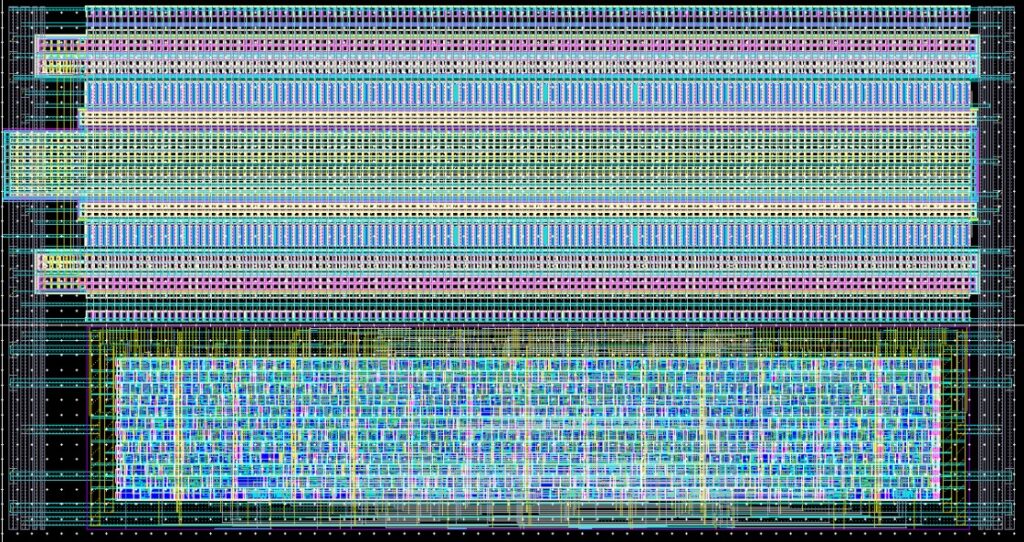

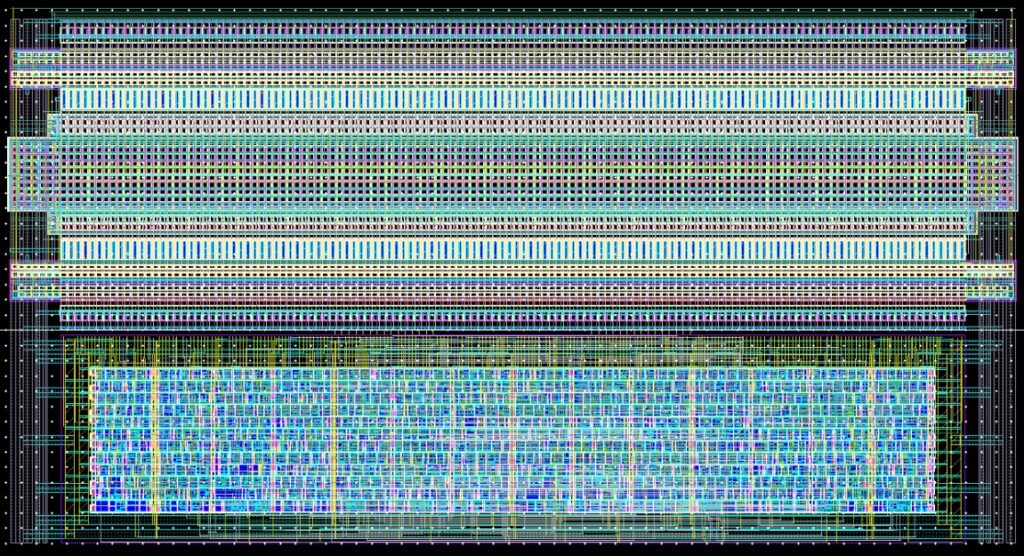

Current-Mode Analog-to-Digital Converter (iADC) Series: The iADC series comprises a patented line of asynchronous current-mode analog-to-digital converters developed for ultra-low-power and cost-efficient applications. Manufactured using standard digital CMOS processes, these converters are designed for continuous, efficient monitoring, supporting smart IoT and near-sensor AI systems.

The iADC converters provide direct interfacing with current-generating sensors, making them well-suited for “always-on” applications and adaptable for current-mode analog neural networks. Initial simulation data is available in preliminary datasheets, with prototypes expected availability by Q1 2025. Evaluation results will follow.

For more information or to request testing, contact sales@ailinear.com.

Common Traits of the iADC Family of IP:

- Fast Dynamic Response: Inherent small voltage swings in current-mode signal processing enhance speed.

- Programmable Conversion Speed: Adjustable IDD enables customizable iADC conversion rates.

- Flexible Transfer Function: Programmable reference network allows for linear or non-linear responses.

- Asynchronous Operation: Clock-free and switch-capacitor-free, eliminating related noise and substrate injections.

- Multi-Channel Configurations: Enhanced matching, compact size, and increased speed using patented RBN technology.

- Concurrent Analog & Digital Computation: Mitigates accuracy loss at higher input frequencies.

- No Passive Components: Eliminates capacitors and resistors, reducing silicon costs and enabling ultra-low current operation.

- Broad/Mainstream Digital CMOS Compatibility: Suitable for production on trailing-to-bleeding-edge digital CMOS processes.

- Enhanced Linearity: Calibration or trimming improves accuracy.

- Protected IP: All iADC topologies in this series are patented.

Current-Mode A/D Converter (iADC) Table Simulation Summary (Silicon being Evaluated)

Silicon evaluation work in progress. Data below are based on simulations.

Refer to each cell data sheet below for more details (please see disclaimers).

| Cell Name | TSMC Fab Node | ~Cell Size (µm×µm) | Bits | aVDD High (v) | aVDD Low (v) | IDD (nA) | INL (LSB) | Gain Error (LSB) | AINBW (KHz) | Ƭ (μS) |

|---|---|---|---|---|---|---|---|---|---|---|

| iADC3_1 | 180nm | 420x180 | 8 | 2 | 1 | 770 | ±1.5 | ±5 | tbd | 8 |

| iADC3_2 | 180nm | 580x220 | 8 | 2 | 1 | 1155 | ±2.5 | ±10 | tbd | 38 |

| iADC3_3 | 180nm | 250x230 | 8 | 2 | 1 | 880 | ±1.25 | ±5 | tbd | 25 |

| iAMP3_4 | 180nm | 290x240 | 8 | 2 | 1 | 885 | ±1.5 | ±10 | tbd | 38 |

| iADC4_1 | 180nm | 190x160 | 8 | 2 | 1 | 452 | ±2.3 | ±5 | tbd | 22 |

| iADC4_2 | 180nm | 205x140 | 8 | 2 | 1 | 680 | ±2.3 | ±5 | tbd | 33 |

| iADC4_3 | 180nm | 345x180 | 8 | 2 | 1 | 2100 | ±0.5 | ±6 | tbd | 4 |

| iADC4_4 | 180nm | 335x180 | 8 | 2 | 1 | 850 | ±0.7 | ±4 | tbd | 5 |

Notes: AINBW denotes iADC’s input 3dB bandwidth. Ƭ denotes the transient response of iADC when AIN is pulsed from ¼ scale to ¾ scale. aVDD high and aVDD low denote the maximum and minimum operating range of analog VDD. All iADC Fabricated in low-cost 180nm Digital CMOS. TBD denotes Testing in progress: temperature = 27C, Analog aVDD = 2v, dVDD = 1v. Digital outputs 0→1v. All iADC asynchronous (no clock and no dynamic IDD when AIN not changing)

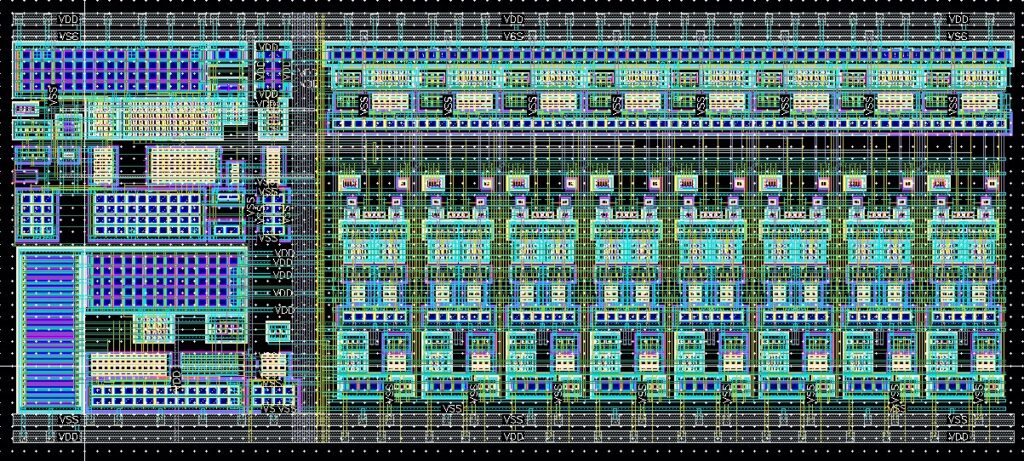

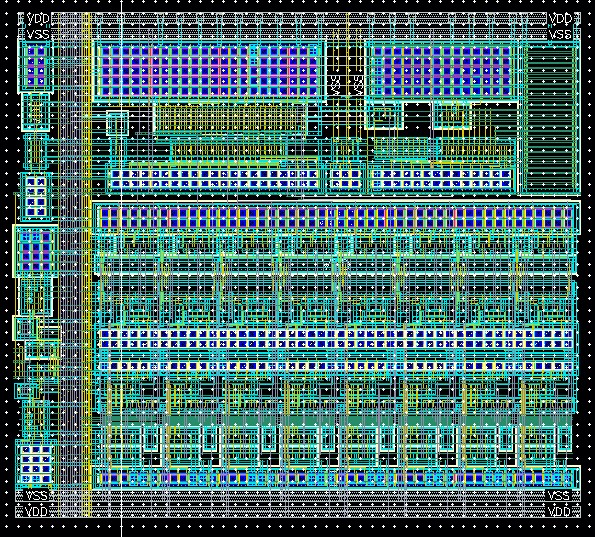

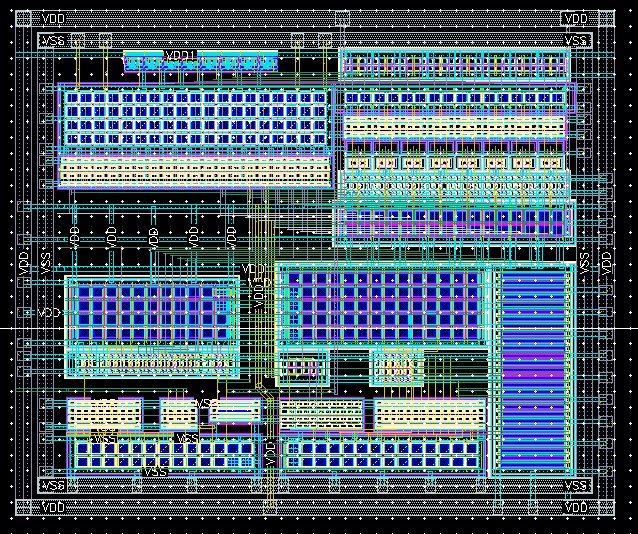

iADC3_1: (silicon available & under test)

- View Datasheet

- Patented ripple current iADC.

- Gray-code signaling enhances accuracy and speed, reducing power consumption (IDD), footprint, and cost.

- Optional: Programmable internal IREF customizes IIN peak-to-peak ranges, supporting range calibration via IREF output.

- Optional: Digital output port (DOUT) can be serialized as needed.

- Digital power consumption reduces dynamically in steady-state IIN conditions, enabled by asynchronous iADC architecture.

- iADC includes power-down (PD) and IIN current source compliance (VCM) voltage setting capabilities.

iADC3_2: (silicon available & under test)

- View Datasheet

- Patented sub-ranging current iADC. Most-Significant-Portion (MSP) of iADC’s first stage reference network inherently enhances the accuracy of the overall iADC

- Programmable internal IREF customizes IIN peak-to-peak ranges, supporting range calibration via IREF

- Digital output port (DOUT) can be serialized as needed.

- Digital power consumption reduces dynamically in steady-state IIN conditions, enabled by asynchronous iADC architecture.

- iADC includes power-down (PD) and IIN current source compliance (VCM) voltage setting capabilities.

iADC3_3: (silicon available & under test)

- View Datasheet

- Gray-code current signaling enhances accuracy and speed, reducing power consumption (IDD), footprint, and cost.

- Optional: Programmable internal IREF customizes IIN peak-to-peak ranges, supporting range calibration via IREF

- Optional: Digital output port (DOUT) can be serialized as needed.

- Digital power consumption reduces dynamically in steady-state IIN conditions, enabled by asynchronous iADC architecture.

- iADC includes power-down (PD) and IIN current source compliance (VCM) voltage setting capabilities.

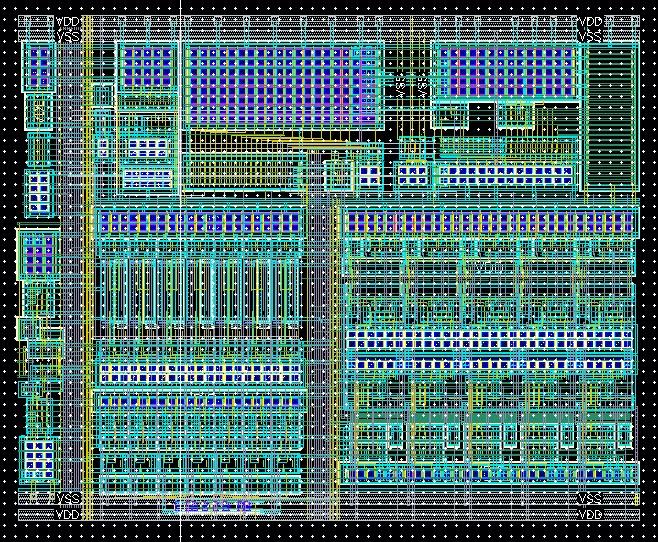

iADC3_4: (silicon available & under test)

- View Datasheet

- Patented segmented sub-ranging iADC. Thermometer-based Most-Significant-Portion (MSP) of iADC’s first stage reference network inherently enhances the accuracy of the overall iADC

- Optional: Programmable internal IREF customizes IIN peak-to-peak ranges, supporting range calibration via IREF

- Optional: Digital output port (DOUT) can be serialized as needed.

- Digital power consumption reduces dynamically in steady-state IIN conditions, enabled by asynchronous iADC architecture.

- iADC includes power-down (PD) and IIN current source compliance (VCM) voltage setting capabilities.

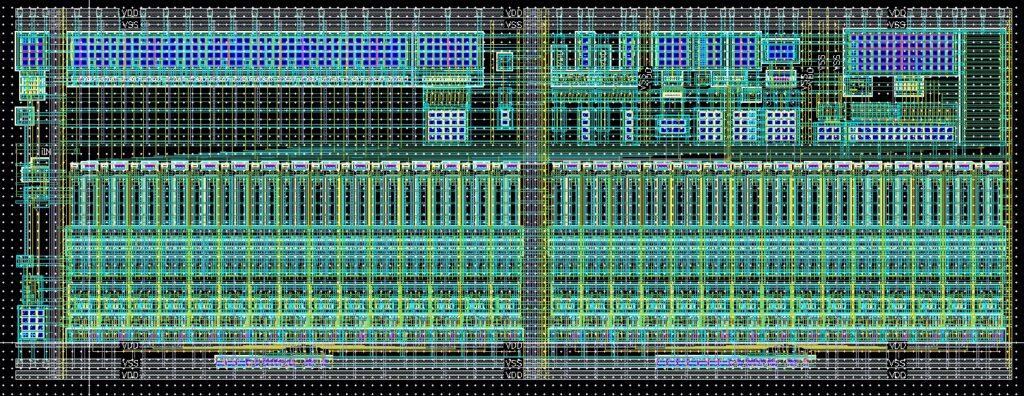

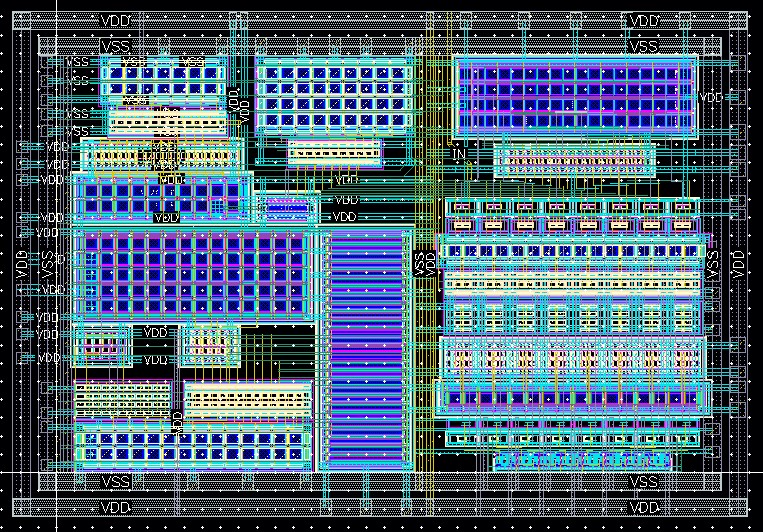

iADC4_1: (silicon available & under test)

- View Datasheet

- Patent pending N-Type Gray-code signaling enhances accuracy and speed, reducing power consumption (IDD), footprint, and cost.

- Optional: Programmable internal IREF customizes IIN peak-to-peak ranges, supporting range calibration via IREF

- Optional: Digital output port (DOUT) can be serialized as needed.

- Digital power consumption reduces dynamically in steady-state IIN conditions, enabled by asynchronous iADC architecture.

- iADC includes power-down (PD) capabilities.

iADC4_2: (silicon available & under test)

- View Datasheet

- Patent pending P-Type Gray-code signaling enhances accuracy and speed, reducing power consumption (IDD), footprint, and cost.

- Optional: Programmable internal IREF customizes IIN peak-to-peak ranges, supporting range calibration via IREF

- Optional: Digital output port (DOUT) can be serialized as needed.

- Digital power consumption reduces dynamically in steady-state IIN conditions, enabled by asynchronous iADC architecture.

- iADC includes power-down (PD) capabilities.

iADC4_3: (silicon available & under test)

- View Datasheet

- Patent N-Type iADC with Pseudo-FLASH architecture enhances accuracy and speed, reducing power consumption (IDD), footprint, and cost.

- The iADC is Inherently Monotonic, with Bubble Error Correction

- Optional: Digital output port (DOUT) can be serialized as needed.

- Digital power consumption reduces dynamically in steady-state IIN conditions, enabled by asynchronous iADC architecture.

- iADC includes power-down (PD) capabilities.

iADC4_4: (silicon available & under test)

- View Datasheet

- Patent P-Type iADC with Pseudo-FLASH architecture enhances accuracy and speed, reducing power consumption (IDD), footprint, and cost.

- The iADC is Inherently Monotonic, with Bubble Error Correction

- Optional: Digital output port (DOUT) can be serialized as needed.

- Digital power consumption reduces dynamically in steady-state IIN conditions, enabled by asynchronous iADC architecture.

- iADC includes power-down (PD) capabilities.