# vADC5\_S\_T work in progress

#### Differential SAR-Based Voltage-Mode Synchronous ADC with S/H

Proof of silicon due 1Q25 | Simulation results below

| Parameter (units)                             | Typical<br>Simulation    | <b>Typical Conditions:</b> $V_{DD}$ =1v, Temperature = 27C, unless otherwise stated. Operating $V_{DD}$ high |

|-----------------------------------------------|--------------------------|--------------------------------------------------------------------------------------------------------------|

|                                               | Spec                     | ≈1v, Operating V <sub>DD</sub> low ≈TBD,                                                                     |

| Resolution (Bits)                             | 8                        |                                                                                                              |

| Differential V <sub>IN</sub> peak-to-peak (v) | $0 { ightarrow} V_{REF}$ | V <sub>REF</sub> P ≈1v & V <sub>REF</sub> N ≈0v, V <sub>CM</sub> ≈ 0.5xV <sub>DD</sub>                       |

| I <sub>DD</sub> (μA)                          | ~1.1                     | $f_{S/H} \approx 40 \text{KHz}$                                                                              |

| ENOB (bits)                                   | ~7.5                     | V <sub>IN</sub> sweep 0→Full-Scale                                                                           |

| Gain Error (%)                                | ~30                      | V <sub>IN</sub> sweep 0→Full-Scale                                                                           |

| Input Bandwidth = AIN <sub>BW</sub> (KHz)     | 25                       | -3dB frequency                                                                                               |

| f <sub>S/H</sub> max (KHz)                    | tbd                      | 1-bit Loss of ENOB                                                                                           |

| Digital I/O Levels (v)                        | $0 \rightarrow V_{DD}$   |                                                                                                              |

| Cell Size (μm X μm)                           | ~127x64                  |                                                                                                              |

| TSMC Process Node (nm)                        | 65                       |                                                                                                              |

<sup>\*</sup>See Disclaimers\*

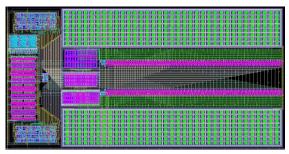

## vADC +S/H Cell Layout

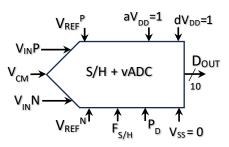

### vADC +S/H Block Diagram

#### **Features:**

- 8-bit resolution, Low-Power, Differential voltage-input, Synchronous vADC with S/H & Power-Down

- Optional: Digital output port (D<sub>OUT</sub>) can be serialized as needed.

- Digital power consumption reduces dynamically in steady-state V<sub>IN</sub> conditions, enabled by asynchronous vADC architecture.

- $V_{IN}P$  and  $V_{IN}N$  terminals swing ~1v Peak-to-Peak around common mode voltage (e.g.,  $V_{CM} \approx 0.5 \times V_{DD}$ )

- Operating condition example: V<sub>REF</sub>P ≈ 1v and V<sub>REF</sub>N ≈ 0v