## VREF2 (internal #chip1\_DTMOST2)

Ultra-Low-Power Fractional Voltage Reference with low TC. Proof of silicon with typical/preliminary measurements available.

Please contact <a href="mailto:sales@ailinear.com">sales@ailinear.com</a> for more information & order specific evaluation

| Parameter                | Typical | Condition                                        |

|--------------------------|---------|--------------------------------------------------|

|                          | Spec    |                                                  |

| I <sub>DD</sub> (nA)     | ~25     | V <sub>DD</sub> =2v, Temperature = 27C           |

| V <sub>DD</sub> Low (v)  | ~0.7    | V <sub>DD</sub> sweep 0v→2.2v, Temperature = 27C |

| V <sub>DD</sub> High (v) | ~2      | V <sub>DD</sub> sweep 0v→2.2v, Temperature = 27C |

| VREF <sub>OUT</sub> (v)  | ~0.43   | V <sub>DD</sub> =2v, Temperature = 27C           |

| TC (PPM/C)               | ~350    | V <sub>DD</sub> =2v, ΔT ~30C                     |

| PSRR (dB)                | ~76     | V <sub>DD</sub> sweep 1v→2.2v, Temperature = 27C |

\*See Disclaimer\*

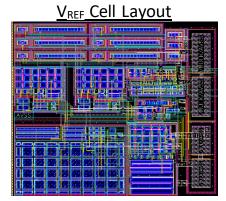

V<sub>REF</sub> Cell Size ~100μm×85 μm in TSMC 180nm CMOS

## Features:

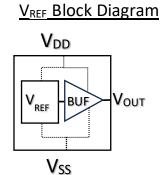

- Small CMOS (~100 $\mu$ m×85  $\mu$ m) bandgap voltage reference ( $V_{OUT} \approx V_{REF} \approx 0.43$ ) Intellectual Property (IP) cell operates in subthreshold with ultra-low  $I_{DD}$  (typical 25nA)

- Patented Low noise design to generate proportional to absolute voltage (V<sub>PTAT</sub>) without resistors

- Equipped with start-up, power-down, and TC trim capability

- Includes an internal buffer (BUF) to drive larger loads (e.g. Mega  $\Omega$ s) in a SoC

- No clock, no switch-capacitor, and no related noise or injections into substrate

- Operating in subthreshold and requiring no resistors facilitate small silicon area and operations at ultra-low currents

- Operation at low V<sub>DD</sub> levels ≈V<sub>REF</sub> + 2V<sub>DS</sub>

- Manufacturable on trailing-to-bleeding edge digital CMOS

- Based on 180nm digital CMOS at TSMC and portable to smaller fabrication nodes.