## IBIAS 11A

Ultra-Low-Power Proportional to Absolute Temperature (I<sub>PTAT</sub>) Bias Current Source. Proof of silicon with typical/preliminary measurements available. (Please contact sales@ailinear.com)

| Parameter                | Typical | Condition                                        |

|--------------------------|---------|--------------------------------------------------|

|                          | Spec    |                                                  |

| I <sub>DD</sub> (nA)     | 12      | V <sub>DD</sub> =2v, Temperature = 27C           |

| V <sub>DD</sub> Low (v)  | 0.7     | V <sub>DD</sub> sweep 0v→2.2v, Temperature = 27C |

| V <sub>DD</sub> High (v) | 2       | V <sub>DD</sub> sweep 0v→2.2v, Temperature = 27C |

| TC (%/C)                 | 0.4     | V <sub>DD</sub> =2v, ΔT ~30C                     |

| VC (%/V)                 | 0.4     | V <sub>DD</sub> sweep 1v→2.2v, Temperature = 27C |

\*See Disclaimer\*

## Cell Layout

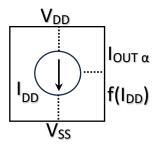

## **Block Diagram**

Cell Size ~68μm×52 μm in TSMC 180nm CMOS

## Features:

- Patented

- Programmable (pre or post silicon) I<sub>OUT</sub> that tracks I<sub>DD</sub>

- Tiny CMOS (~68μm×52 μm) bias current Intellectual Property (IP) cell operating in subthreshold with ultra-low current consumption I<sub>DD</sub> (typical 12nA)

- Large value but tiny active bias resistor (R<sub>PMOS</sub>) as a function of PMOSFET keeps I<sub>DD</sub> ultra-low

- Most suitable for SoC whose analog (e.g., oscillator, comparator, ADC) performance best correlates with PMOSFET parameters

- Suitable for SoC where I<sub>BIAS</sub> is more optimized when V<sub>SS</sub> coupled with PTAT Kirkoff Voltage Loop (KVL)

- Utilizing PTAT loop with NMOSFETs needing 1V<sub>GS</sub>+2V<sub>DS</sub> for lower V<sub>DD</sub> operating range

- I<sub>DD</sub> and I<sub>OUT</sub> absolute value mostly a function of PMOSFET mobility (μ) inherently more stable to help narrow I<sub>DD</sub> variation over fabrication process corners

- Based on 180nm digital CMOS at TSMC and portable to smaller fabrication nodes.