# **AMP2\_3**

<u>Smart Amplifier</u>: Ultra-Low-Power, Low-Noise, High-Gain, Near Rail-To-Rail input/output (I/O), Moderate-Speed Buffer Amplifier. Proof of silicon with typical/preliminary measurements available.

Please contact <a href="mailto:sales@ailinear.com">sales@ailinear.com</a> for more information & ordering specific evaluation.

| Parameter                | Typical Spec | <b>Typical Conditions:</b> V <sub>DD</sub> =1v, Temperature = 27C,        |

|--------------------------|--------------|---------------------------------------------------------------------------|

|                          |              | unless otherwise stated                                                   |

| I <sub>DD</sub> (nA)     | ~73          | sAMP Gain=1 & V <sub>INPUT</sub> ≈ 0.5 V <sub>DD</sub>                    |

| V <sub>DD</sub> Low (v)  | ~0.8         | V <sub>DD</sub> sweep 0v→1v                                               |

| V <sub>DD</sub> High (v) | ~1           | V <sub>DD</sub> sweep 0v→1v                                               |

| V <sub>OFFSET</sub> (mv) | ~±5          | sAMP Gain=1 & V <sub>INPUT</sub> ≈ 0.5 V <sub>DD</sub>                    |

| I/O Swing to Rails (mv)  | ~±25         | V <sub>DD</sub> sweep 0v→2v                                               |

| Gain (dB)                | ~90          | sAMP Gain=1 & V <sub>INPUT</sub> ≈ 0.5 V <sub>DD</sub> . Tested at higher |

|                          |              | frequencies and extrapolated to DC                                        |

| PSRR (dB)                | ~80          | sAMP Gain=1 & V <sub>INPUT</sub> ≈ 0.5 V <sub>DD</sub> . Tested at higher |

|                          |              | frequencies and extrapolated to DC                                        |

| Noise (μν/√Hz)           | ~7           | $V_{OUT}$ noise 10Hz. sAMP Gain=1 & $V_{INPUT} \approx 0.5 V_{DD}$ .      |

| fu (KHz)                 | ~7           | sAMP Gain=1 & 10mv p-p V <sub>INPUT</sub> mid ≈ 0.5 V <sub>DD</sub>       |

| SR (v/ms)                | ~170         | sAMP Gain=1 & 0.8v p-p pulse V <sub>INPUT</sub> mid ≈ 0.5 V <sub>DD</sub> |

| ts (μs)                  | ~20          | sAMP Gain=1 & 0.8v p-p pulse V <sub>INPUT</sub> mid ≈ 0.5 V <sub>DD</sub> |

| Cell Size (μm X μm)      | ~115x100     |                                                                           |

| TSMC Process Node (nm)   | 65           |                                                                           |

#### \*See Disclaimers\*

### sAMP Cell Layout

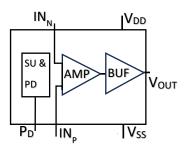

## sAMP Block Diagram

#### Features:

- The sAMP's I<sub>Q</sub> ≈ f(PTAT) → improved dynamic response's TC

- The  $I_{DD} \approx f(I_Q) \approx f(\mu_{NMOS}) \approx f(R_{NMOS}) \neq f(V_{TH}) \rightarrow I_{DD}$  less sensitive to manufacturing variations

- The R<sub>NMOS</sub> inside PTAT voltage loop coupled to V<sub>SS</sub> for less sensitivity to V<sub>DD</sub> noise

- At ultra-low I<sub>DD</sub>, utilizing standard cascoded current mirrors in FCTA stage

- The sAMP with internal class AB (push-pull) buffer (BUF) can drive larger loads (e.g. 10s of mega Ωs) in a low-power SoC